硬件產(chǎn)品開發(fā)總結(jié)(二) 硬件開發(fā)的流程、挑戰(zhàn)與最佳實(shí)踐

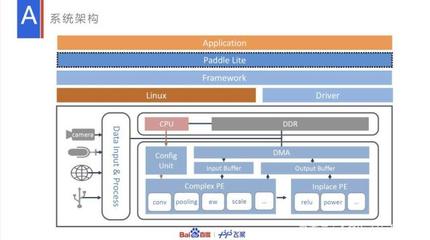

在硬件產(chǎn)品開發(fā)的宏大藍(lán)圖中,硬件開發(fā)是承上啟下的核心階段。它將前期的概念設(shè)計(jì)、需求分析與架構(gòu)規(guī)劃,轉(zhuǎn)化為實(shí)實(shí)在在、可測試、可生產(chǎn)的物理實(shí)體。本部分將系統(tǒng)性地硬件開發(fā)的關(guān)鍵流程、常見挑戰(zhàn)與應(yīng)對策略,為開發(fā)者提供清晰的實(shí)踐指引。

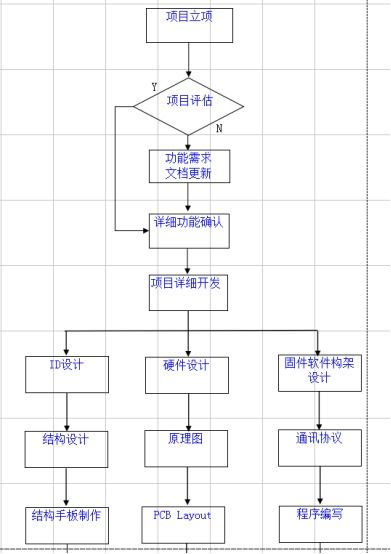

一、硬件開發(fā)的核心流程

硬件開發(fā)并非簡單的“畫板子、做樣品”,而是一個(gè)嚴(yán)謹(jǐn)?shù)摹⒍嗟墓こ踢^程。其典型流程可分為以下幾個(gè)階段:

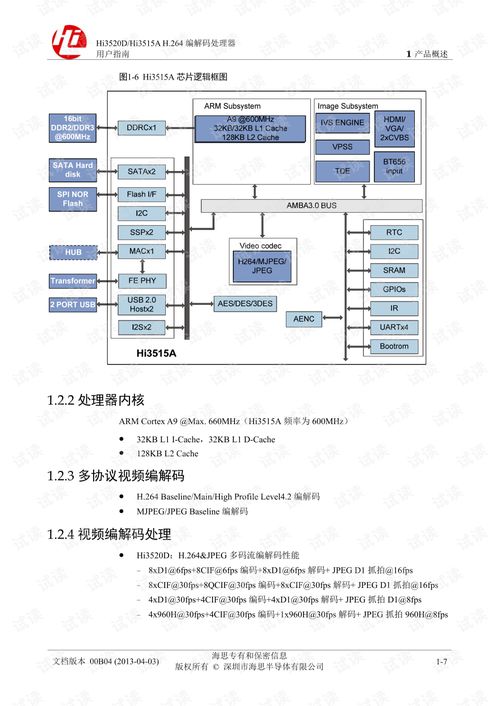

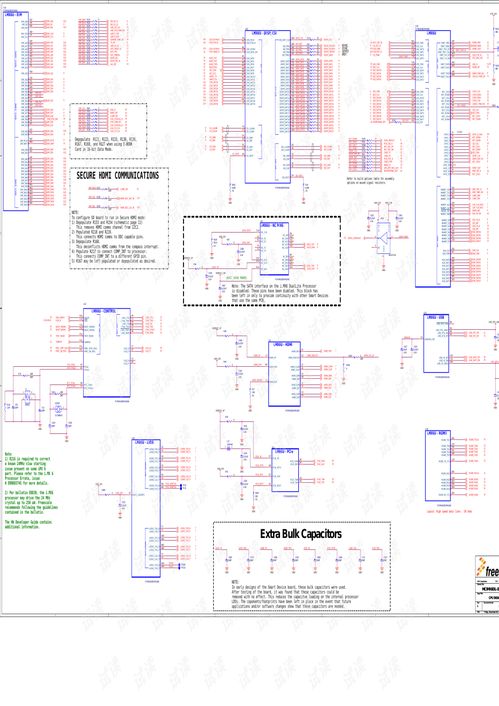

- 詳細(xì)設(shè)計(jì)與元器件選型:基于產(chǎn)品規(guī)格書(PRD)和系統(tǒng)架構(gòu),進(jìn)行詳細(xì)的原理圖設(shè)計(jì)。此階段的核心挑戰(zhàn)在于元器件選型——需要在性能、成本、功耗、供貨周期、可靠性及可獲得性(如車規(guī)級、工業(yè)級)之間取得最佳平衡。建立并維護(hù)一個(gè)經(jīng)過驗(yàn)證的“優(yōu)選元器件庫”至關(guān)重要。

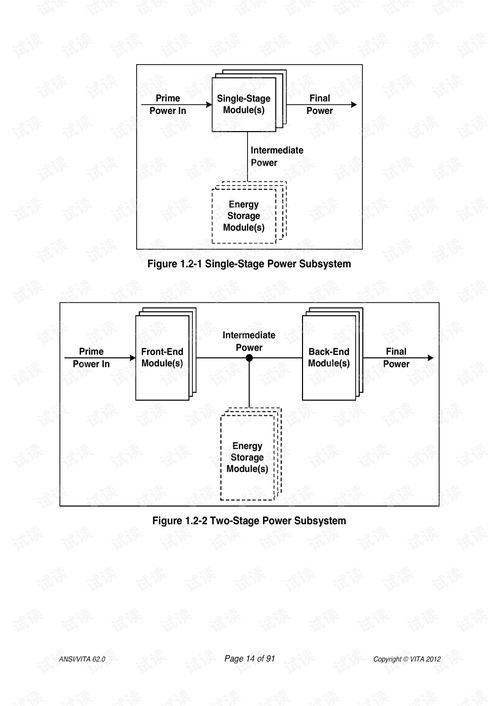

- PCB設(shè)計(jì)與仿真:將原理圖轉(zhuǎn)化為PCB布局。這不僅是連線的藝術(shù),更是電磁兼容(EMC)、信號完整性(SI)、電源完整性(PI)和熱管理的綜合博弈。關(guān)鍵工作包括:層疊設(shè)計(jì)、高速信號線(如DDR, PCIe)的拓?fù)渑c等長處理、電源分割、去耦電容的優(yōu)化布局、以及地平面的完整性。前期利用仿真工具(如SI/PI仿真)預(yù)測問題,能大幅減少后期調(diào)試的試錯成本。

- 原型(EVT)制作與調(diào)試:發(fā)出首版(V1.0)PCB進(jìn)行打樣與貼片,組裝成工程原型機(jī)。調(diào)試階段是發(fā)現(xiàn)問題、驗(yàn)證設(shè)計(jì)的開始。開發(fā)者需要系統(tǒng)地進(jìn)行電源上電時(shí)序與紋波測試、時(shí)鐘與復(fù)位信號質(zhì)量測試、關(guān)鍵接口(如USB, Ethernet)功能測試,并使用示波器、邏輯分析儀等工具定位故障。詳細(xì)的調(diào)試記錄是寶貴的知識資產(chǎn)。

- 設(shè)計(jì)驗(yàn)證測試(DVT)與可靠性驗(yàn)證:在原型功能基本正常后,進(jìn)入嚴(yán)格的DVT階段。此階段目標(biāo)在于全面驗(yàn)證產(chǎn)品是否符合所有設(shè)計(jì)規(guī)格與行業(yè)標(biāo)準(zhǔn)。測試內(nèi)容包括但不限于:環(huán)境應(yīng)力測試(高低溫、濕度)、機(jī)械應(yīng)力測試(振動、跌落)、長時(shí)間老化測試、EMC預(yù)兼容測試、安規(guī)測試以及完整的系統(tǒng)功能與性能測試。任何在此階段發(fā)現(xiàn)的問題都必須回溯到設(shè)計(jì)端進(jìn)行根因分析并修改。

- 設(shè)計(jì)固化與轉(zhuǎn)產(chǎn)準(zhǔn)備(PVT):當(dāng)設(shè)計(jì)通過DVT驗(yàn)證后,進(jìn)入小批量試產(chǎn)階段。此階段的目標(biāo)是驗(yàn)證制造流程、夾具、測試方案及供應(yīng)鏈的穩(wěn)定性,確保產(chǎn)品能以一致的良率大規(guī)模生產(chǎn)。需要輸出全套的生產(chǎn)制造文件(Gerber, BOM, 裝配圖,測試程序等)并完成對工廠的技術(shù)交底。

二、硬件開發(fā)中的主要挑戰(zhàn)與應(yīng)對

- 跨領(lǐng)域協(xié)同復(fù)雜:現(xiàn)代硬件產(chǎn)品是軟硬件的高度集成。硬件開發(fā)者必須與結(jié)構(gòu)、軟件、射頻、測試、供應(yīng)鏈團(tuán)隊(duì)緊密協(xié)作。建立清晰的接口文檔(如引腳定義、通信協(xié)議)、定期的協(xié)同會議以及使用協(xié)同管理工具(如Jira, Confluence)是保障項(xiàng)目順暢的關(guān)鍵。

- 信號與電源完整性挑戰(zhàn):隨著處理器速度提升和供電電壓降低,SI/PI問題日益突出。最佳實(shí)踐包括:在布局前制定詳細(xì)的布線約束規(guī)則;對關(guān)鍵網(wǎng)絡(luò)進(jìn)行仿真;采用多層板并為關(guān)鍵電源與地提供完整平面;在電源入口和芯片電源引腳附近合理布置不同容值的去耦電容。

- 熱設(shè)計(jì)與管理:功耗帶來發(fā)熱,過熱導(dǎo)致性能下降乃至損壞。需從系統(tǒng)層面考慮散熱:合理布局高熱器件、使用熱仿真優(yōu)化散熱路徑、選擇有效的散熱方案(如散熱片、風(fēng)扇、熱管)、并在結(jié)構(gòu)設(shè)計(jì)上預(yù)留風(fēng)道。

- 可測試性設(shè)計(jì)(DFT)與可生產(chǎn)性設(shè)計(jì)(DFM):為后期測試和生產(chǎn)便利,應(yīng)在設(shè)計(jì)初期就融入DFT/DFM思想。例如,添加關(guān)鍵的測試點(diǎn)、JTAG接口;考慮PCB的工藝邊、拼板方式、元器件的封裝是否便于自動化貼裝等。與制造廠的早期溝通能有效避免此類問題。

- 變更管理與成本控制:開發(fā)過程中的設(shè)計(jì)變更是常態(tài),但必須被嚴(yán)格管理。任何變更都應(yīng)評估其對成本、 schedule和已生產(chǎn)物料的影響。使用版本控制工具管理原理圖與PCB文件,并確保BOM的每一次變更都有據(jù)可查。

三、給硬件開發(fā)者的建議

- 文檔至上:從設(shè)計(jì)規(guī)范、評審記錄到調(diào)試報(bào)告,詳盡及時(shí)的文檔是團(tuán)隊(duì)協(xié)作和知識傳承的基石。

- 仿真先行:在資金和時(shí)間允許的情況下,盡可能在投板前進(jìn)行仿真,將問題消滅在圖紙階段。

- 模塊化與復(fù)用:將經(jīng)過驗(yàn)證的電路模塊(如電源、MCU最小系統(tǒng))標(biāo)準(zhǔn)化、模塊化,能顯著提升后續(xù)項(xiàng)目的開發(fā)效率與可靠性。

- 擁抱調(diào)試:調(diào)試是硬件工程師的核心能力。保持耐心,遵循“由大到小、由電源到信號”的系統(tǒng)化排查思路,并善用儀器設(shè)備的進(jìn)階功能。

- 保持好奇心與持續(xù)學(xué)習(xí):新技術(shù)、新器件、新工藝不斷涌現(xiàn)。關(guān)注行業(yè)動態(tài),理解底層原理,才能設(shè)計(jì)出更具競爭力的產(chǎn)品。

硬件開發(fā)是一場需要精密規(guī)劃、嚴(yán)謹(jǐn)執(zhí)行和持續(xù)優(yōu)化的“持久戰(zhàn)”。成功的硬件產(chǎn)品,其背后必然是一套融合了創(chuàng)新設(shè)計(jì)、工程嚴(yán)謹(jǐn)性與供應(yīng)鏈智慧的完整開發(fā)體系。當(dāng)硬件平臺穩(wěn)定可靠地搭建起來,它便為軟件的精彩演繹提供了最堅(jiān)實(shí)的舞臺。

如若轉(zhuǎn)載,請注明出處:http://www.wdrmgkay.cn/product/31.html

更新時(shí)間:2026-04-14 09:53:40